The semiconductor production process is one of the most complex manufacturing workflows ever developed. It transforms purified silicon into highly integrated circuits containing billions of transistors, powering everything from automotive ECUs to industrial IoT gateways and medical devices.

For engineering leaders and embedded system architects, understanding how semiconductor fabrication works is not merely academic. It directly influences component selection, lifecycle planning, supply chain risk, reliability engineering, and long-term product strategy. Process nodes, yield constraints, packaging technologies, and testing methodologies all affect performance, power consumption, availability, and cost.

This article provides a structured, technical deep dive into the semiconductor production process: from raw silicon to packaged integrated circuits, focusing on what matters for product development teams building reliable embedded systems.

Overview of the Semiconductor Production Process

At a high level, the semiconductor manufacturing flow consists of:

- Silicon purification and wafer production.

- Wafer fabrication (front-end processing).

- Wafer probing and electrical testing.

- Dicing and packaging (back-end processing).

- Final testing and qualification.

Each step requires extreme precision, often at nanometer-scale tolerances, inside ultra-clean facilities (fabs) with strict contamination control.

1. Silicon Purification and Wafer Production

The process begins with silicon derived from quartz (SiO₂). Through chemical refinement (typically the Siemens process), manufacturers produce electronic-grade polysilicon with impurity levels below one part per billion.

Using the Czochralski (CZ) method, a single-crystal silicon ingot is grown by slowly pulling a seed crystal from molten silicon. This produces a cylindrical crystal structure with highly controlled orientation and minimal defects.

The ingot is then:

- sliced into thin wafers (typically 150 mm, 200 mm, or 300 mm),

- polished to atomic-level flatness,

- chemically cleaned.

These wafers form the substrate for integrated circuit manufacturing.

2. Wafer Fabrication (Front-End Processing)

Wafer fabrication is the core of the semiconductor production process. It involves repeatedly building and patterning thin layers to create transistors and interconnects.

Key Steps in Wafer Fabrication

Oxidation

A thin silicon dioxide (SiO₂) layer is thermally grown on the wafer surface. This layer acts as an insulator or gate dielectric.

Photolithography

Photolithography transfers circuit patterns onto the wafer:

- Apply photoresist.

- Expose through a photomask using deep ultraviolet (DUV) or extreme ultraviolet (EUV) light.

- Develop the resist.

- Etch exposed areas.

This step defines transistor gates, diffusion regions, and metal interconnect layers.

Doping (Ion Implantation)

Controlled impurities (e.g., boron, phosphorus, arsenic) are implanted into silicon to create:

- P-type regions

- N-type regions

This step defines transistor characteristics such as threshold voltage and carrier mobility.

Deposition

Thin films are added using techniques such as:

- Chemical Vapor Deposition (CVD)

- Physical Vapor Deposition (PVD)

- Atomic Layer Deposition (ALD)

These layers may form:

- Gate materials

- Dielectrics

- Interconnect metals

Etching

Unwanted material is removed using:

- Wet chemical etching

- Plasma (dry) etching

Chemical Mechanical Planarization (CMP)

CMP ensures the wafer surface remains flat after multiple layer additions, critical for sub-10 nm nodes.

Front-End Process Complexity

Modern chips may require:

- 50-100+ mask layers

- Hundreds of processing steps

- Nanometer-scale alignment accuracy

- Sub-angstrom film thickness control

Yield management is critical. Even minor particle contamination can destroy entire die regions.

For embedded system companies, node selection (e.g., 180 nm vs. 28 nm vs. 7 nm) significantly affects:

- Cost per wafer

- Power efficiency

- Long-term availability

- Automotive-grade qualification (AEC-Q100)

3. Wafer Probing and Electrical Testing

After fabrication, wafers undergo wafer sort testing.

Using probe cards, automated test equipment (ATE) verifies:

- Basic transistor functionality

- Leakage currents

- Timing characteristics

- Parametric compliance

Defective dies are mapped and excluded from packaging. Yield metrics determine economic viability.

For safety-critical industries (automotive, medical), early screening is crucial for functional safety compliance (ISO 26262).

4. Dicing and Packaging (Back-End Processing)

Dicing

The wafer is cut into individual dies using precision saws or laser cutting.

Packaging

Packaging provides:

- Mechanical protection

- Electrical connectivity

- Thermal management

Common package types:

- QFN (Quad Flat No-Lead)

- BGA (Ball Grid Array)

- WLCSP (Wafer-Level Chip-Scale Package)

- Flip-chip packages

- System-in-Package (SiP)

Advanced packaging trends include:

- 2.5D/3D stacking

- Chiplets

- Through-Silicon Vias (TSVs)

Packaging significantly impacts:

- Thermal dissipation

- EMI behavior

- Signal integrity

- Reliability

This directly affects PCB design and system-level integration decisions.

5. Final Testing and Qualification

Packaged ICs undergo:

- Functional testing

- Burn-in stress testing

- Temperature cycling

- Reliability screening

Automotive and industrial components may require:

- Extended temperature range validation

- HTOL (High-Temperature Operating Life)

- AEC-Q qualification

Only after passing final inspection are components released to distribution.

Applications & Industry Relevance

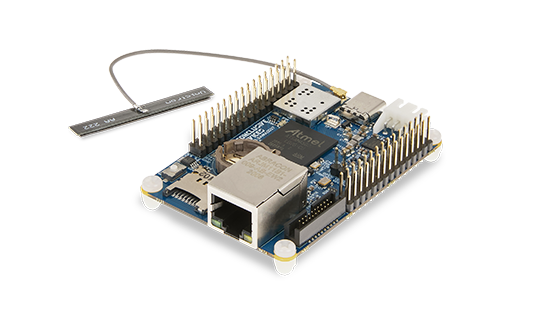

Automotive

Modern vehicles contain 1,000+ semiconductor devices. Applications include:

- ADAS processors

- Power management ICs

- Motor drivers

- Radar front-ends

Node selection must balance performance with long lifecycle availability (10-15+ years).

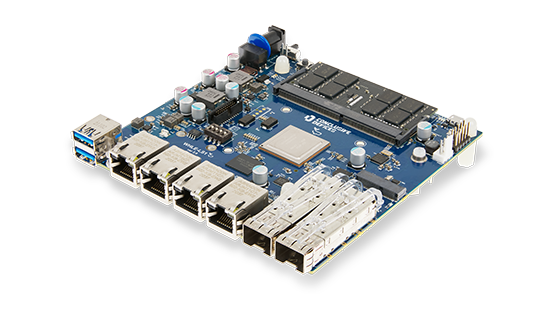

Industrial Automation

PLC systems and edge controllers often rely on mature nodes (90–180 nm) for:

- High reliability

- Long-term supply stability

- Radiation tolerance

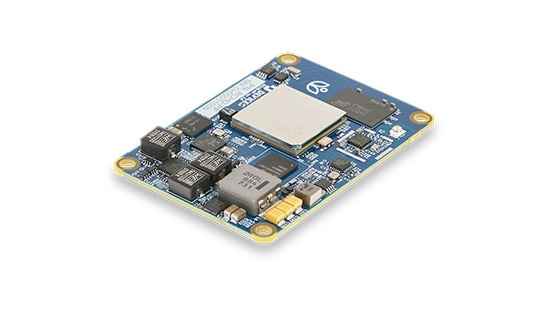

IoT and Edge Devices

Battery-powered IoT devices benefit from:

- Advanced low-power nodes

- Integrated RF transceivers

- System-on-Chip architectures

In these systems, the semiconductor production process influences:

- Leakage current

- Power gating capabilities

- Integration density

For companies developing custom electronics, understanding fabrication constraints is essential during Hardware Design and Firmware Development phases.

Semiconductor Production Process vs. Chip Design

Many engineering teams conflate fabrication with chip design.

| Chip Design | Semiconductor Production Process |

| RTL development | Wafer fabrication |

| Verification & simulation | Photolithography & doping |

| Physical layout | Deposition & etching |

| Tape-out | Manufacturing in fab |

Design decisions directly influence manufacturability (DFM). Poor layout can reduce yield.

Close collaboration between chip designers, hardware architects, and manufacturing partners reduces risk.

Best Practices for Engineering Teams

1. Choose the Right Process Node

- Do not default to the smallest node. Consider:

- Availability

- Cost

- Qualification requirements

- Power vs. complexity trade-offs

2. Plan for Supply Chain Risk

The 2020-2023 semiconductor shortage showed:

- Capacity concentration risk

- Geopolitical exposure

- Lead-time volatility

- Multi-sourcing and lifecycle forecasting are essential.

3. Consider Packaging Early

Thermal constraints and signal routing should influence early system architecture decisions.

4. Align Firmware with Hardware Capabilities

Understanding transistor-level limitations helps optimize:

- Power modes

- Clock scaling

- Peripheral usage

Common Mistakes in Semiconductor-Dependent Product Development

- Selecting cutting-edge nodes for low-volume products.

- Ignoring long-term availability requirements.

- Underestimating thermal constraints.

- Assuming packaging is a minor decision.

- Failing to analyze yield risk in custom ASIC programs.

FAQ: Semiconductor Production Process

How long does semiconductor fabrication take?

Front-end wafer fabrication typically takes 8–12 weeks, depending on complexity and node.

Why are semiconductor fabs so expensive?

Modern fabs cost $10-20+ billion due to:

- EUV lithography systems

- Cleanroom requirements

- Precision process control

What is the difference between front-end and back-end processing?

Front-end: transistor formation on wafer.

Back-end: packaging and final testing.

Why are mature nodes still widely used

They offer:

- Higher reliability

- Lower cost

- Better availability

- Suitability for analog and power applications

Simplified Semiconductor Manufacturing Flow Diagram

Silicon Refinement

↓

Ingot Growth (CZ)

↓

Wafer Slicing & Polishing

↓

Oxidation / Deposition

↓

Photolithography

↓

Etching & Doping

↓

Layer Repetition (50–100 cycles)

↓

Wafer Testing

↓

Dicing

↓

Packaging

↓

Final Test & Qualification

Conclusion

The semiconductor production process is a multi-stage, ultra-precise manufacturing workflow that transforms purified silicon into complex integrated circuits. Its constraints—node technology, yield management, packaging methods, and qualification requirements—directly influence embedded product performance, cost, reliability, and lifecycle stability.

For CTOs and engineering leaders, a working understanding of semiconductor fabrication enables better architectural decisions, smarter supplier negotiations, and more resilient product strategies.

At Conclusive Engineering, we bridge the gap between semiconductor capabilities and real-world embedded system design, helping companies build robust hardware platforms, optimize firmware performance, and deliver reliable products in automotive, industrial, and IoT markets.

If you're planning a hardware platform or evaluating long-term semiconductor strategy, our team can support you from architecture to production readiness.